# SIEMENS

## Nonvolatile Memory 1-Kbit E<sup>2</sup>PROM

## **Preliminary Data**

#### Features

- Word-organized reprogrammable nonvolatile memory in n-channel floating-gate technology (E<sup>2</sup>PROM)

- 128 × 8-bit organization

- Supply voltage 5 V

- Serial 2-line bus for data input and output (I<sup>2</sup>C Bus)

- Reprogramming mode, 10 ms erase/write cycle

- Reprogramming by means of on-chip control (without external control)

- Check for end of programming process

- Data retention > 10 years

- More than 10<sup>4</sup> reprogramming cycles per address

- Compatible with SDA 2516. Exception: Conditions for total erase and current consumption  $I_{\rm CC}$ .

#### **Circuit Description**

#### I<sup>2</sup>C Bus Interface

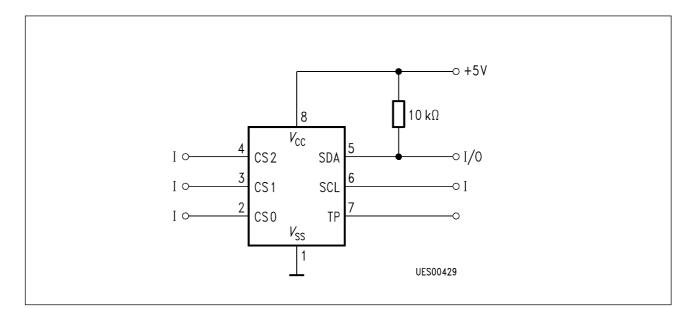

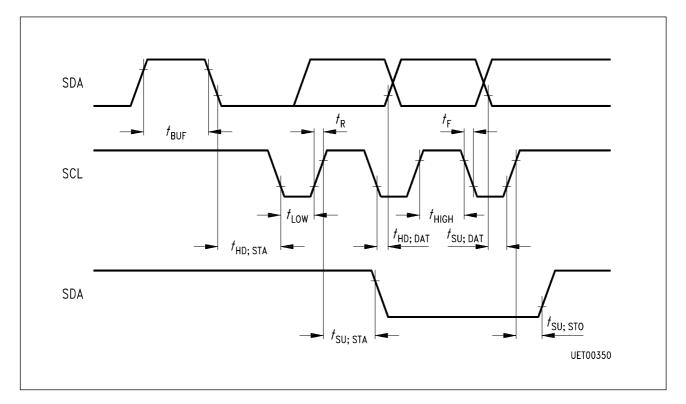

The I<sup>2</sup>C Bus is a bidirectional 2-line bus for the transfer of data between various integrated circuits. It consists of a serial data line SDA and a serial clock line SCL. The data line requires an external pull-up resistor to  $V_{CC}$  (open drain output stage).

The possible operational states of the I<sup>2</sup>C Bus are shown in **figure 1**. In the quiescent state, both lines SDA and SCL are high, i.e. the output stage of the data line is disabled. As long a SCL remains "1", information changes on the data bus indicate the start or the end of data transfer between two components.

The transition on SDA from "1" to "0" is a start condition, the transition from "0" to "1" a stop condition. During a data transfer the information on the data bus will only change while the clock line SCL is "0". The information on SDA is valid as long as SCL is "1".

In conjunction with an I<sup>2</sup>C Bus system, the memory component can operate as a receiver and as a transmitter (slave receiver or slave transmitter). Between a start and stop condition, information is always transmitted in byte-organized form. Between the trailing edge of the eighth clock pulse and

## SDA 2516-5

MOS IC

a ninth acknowledge clock pulse, the memory component sets the SDA line to low as a confirmation of reception, if the chip select conditions have been met. During the output of data, the data output of the memory is high in impedance during the ninth clock pulse (acknowledge master).

The signal timing required for the operation of the  $I^2C$  Bus is summarized in **figure 2**.

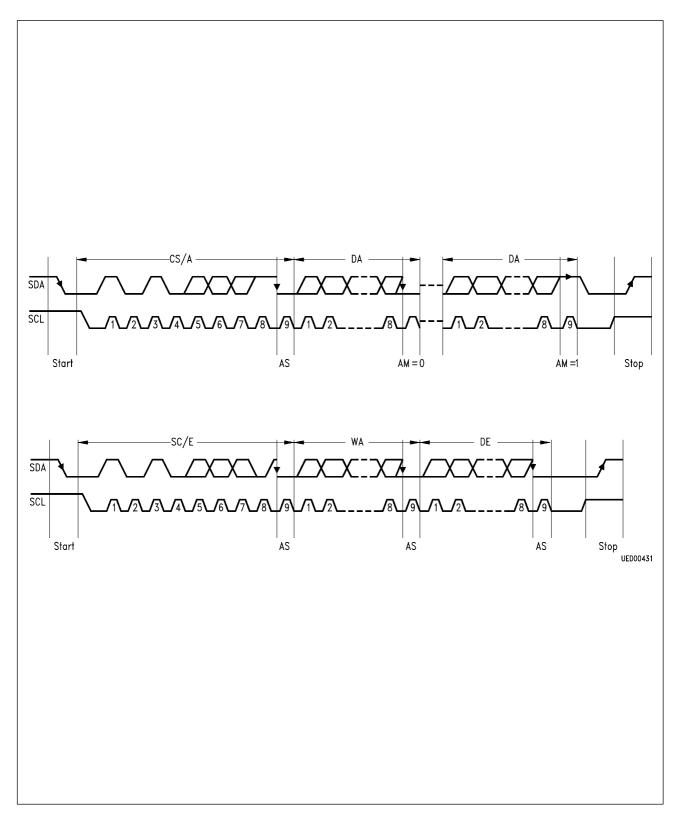

### Control Functions of the I<sup>2</sup>C Bus

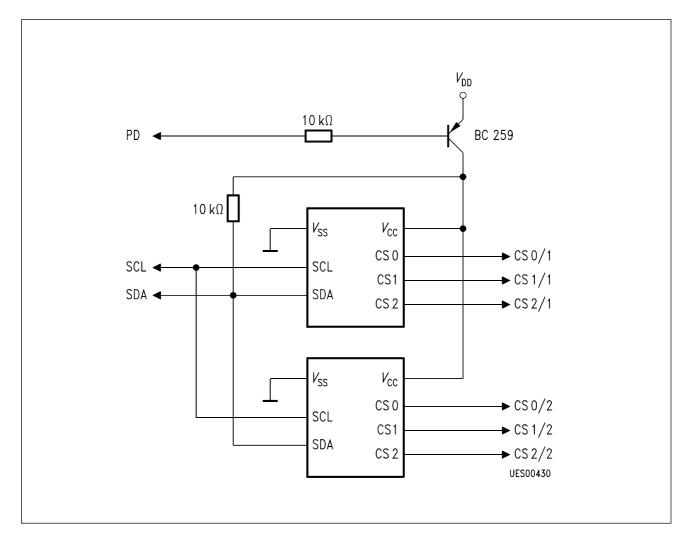

The memory component is controlled by the controller (master) via the I<sup>2</sup>C Bus in two operating modes: read-out cycle, and reprogramming cycle, including erase and write to a memory address. In both operating modes, the controller, as transmitter, has to provide 3 bytes and an additional acknowledge clock pulse to the bus after the start condition. During a memory read, at least nine additional clock pulses are required to accept the data from the memory and the acknowledge master, before the stop condition may follow. In the case of programming, the active programming process is only started by the stop condition after data input (see figure 3).

The chip select word contains the 3 chip select bits CS0, CS1 and CS2, thus allowing 8 memory chips to be connected in parallel. Chip select is achieved when the three control bits logically correspond to the selected conditions at the select inputs.

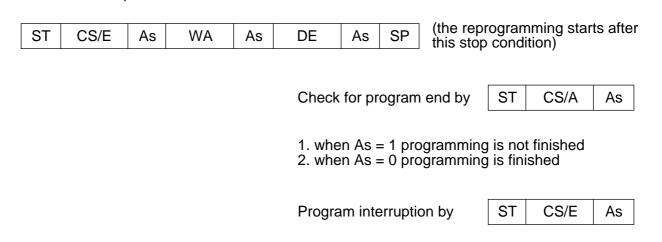

#### Check for End of Programming or Abortion of Programming Process

If the chip is addressed during active reprogramming by entering CS/E, the programming process is terminated. If, however, it is addressed by entering CS/A, the entry will be ignored. Only after programming has been terminated will the chip respond to CS/A. This allows the user to check whether the end of the programming process has been reached (see figure 3).

#### Memory Read

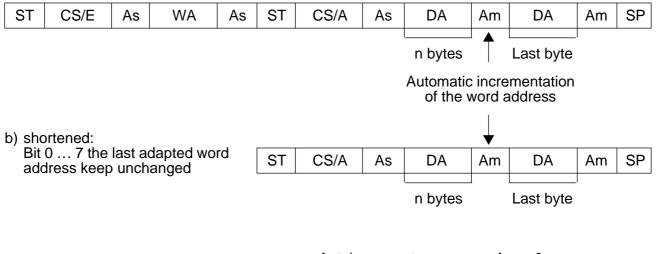

After the input of the first two control words CS/E and WA, the resetting of the start condition and the input of a third control word CS/A, the memory is set ready to read. During acknowledge clock nine, the memory information is transferred in parallel mode to the shift register. Subsequent to the trailing edge of the acknowledge clock, the data output is low impedance and the first data bit can be sampled, **(see figure 4)**.

With every shift clock, an additional bit reaches the output. After reading a byte, the internal address counter is automatically incremented when the master receiver switches the data line to "low" during the ninth clock (acknowledge master). Any number of memory locations can thus be read one after the other. At address 128, an overflow to address 0 is not initiated. With the stop condition, the data output returns to high-impedance mode. The internal sequence control of the memory component is reset from the read to the quiescent with the stop condition.

#### Memory Reprogramming

The reprogramming cycle of a memory word comprises an erase and a subsequent write process. During erase, all eight bits of the selected word are set into "1" state. During write, "0" states are generated according to the information in the internal data register, i.e. according to the third input control word.

After the 27th and the last clock of the control word input, the active programming process is started by the stop condition. The active reprogramming process is executed under onchip control.

The time required for reprogramming depends on component deviation and data patterns. Therefore, with rated supply voltage, the erase/write process extends over max. 20 ms, or more typically, 10 ms. In the case of data word input without write request (write request is defined as data bit in data register set to "0"), the write process is suppressed and the programming time is shortened. During a subsequent programming of an already erased memory address, the erase process is suppressed again, so that the reprogramming time is also shortened.

#### Important: Switch-On Mode and Chip Reset

After the supply voltage  $V_{DD}$  has been connected, the data output will be in the high-impedance mode. As a rule, **the first operating mode** to be entered, should be the **read process of a word address.** As a result of the built-in "power-on reset" circuit, programming requests will not be accepted immediately after the supply voltage has been switched on.

#### **Total Erase**

Enter the control word CS/E, load the address register with address 0 and the data register with FF (hex) to erase the entire contents of the memory. Switch input CS2 to "open" immediately prior to generating the stop condition. The subsequent stop condition triggers a total erase. Upon termination of "total erase", CS2 must be reconnected to either 0 V or  $\ge$  4.5 V.

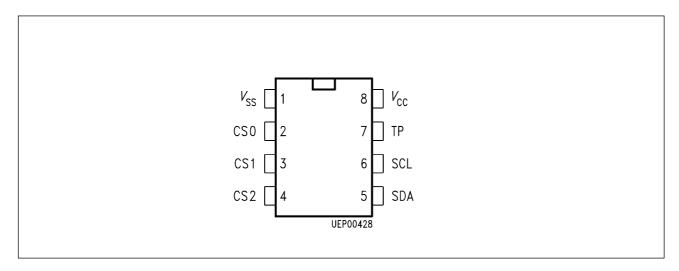

## **Pin Configuration**

(top view)

### **Pin Definitions and Functions**

| Pin No. | Symbol          | Function                                                                                       |  |

|---------|-----------------|------------------------------------------------------------------------------------------------|--|

| 1       | V <sub>SS</sub> | Ground                                                                                         |  |

| 2       | CS0             | Chip select                                                                                    |  |

| 3       | CS1             | Chip select                                                                                    |  |

| 4       | CS2             | Chip select $0 \le V_{I} \le 0.2 V$ ; $4.5 \le V_{I} \le V_{CC}$ , open, total erase condition |  |

| 5       | SDA             | Data line                                                                                      |  |

| 6       | SCL             | Clock line                                                                                     |  |

| 7       | TP              | Test pin                                                                                       |  |

| 8       | V <sub>CC</sub> | Supply voltage                                                                                 |  |

## **SIEMENS**

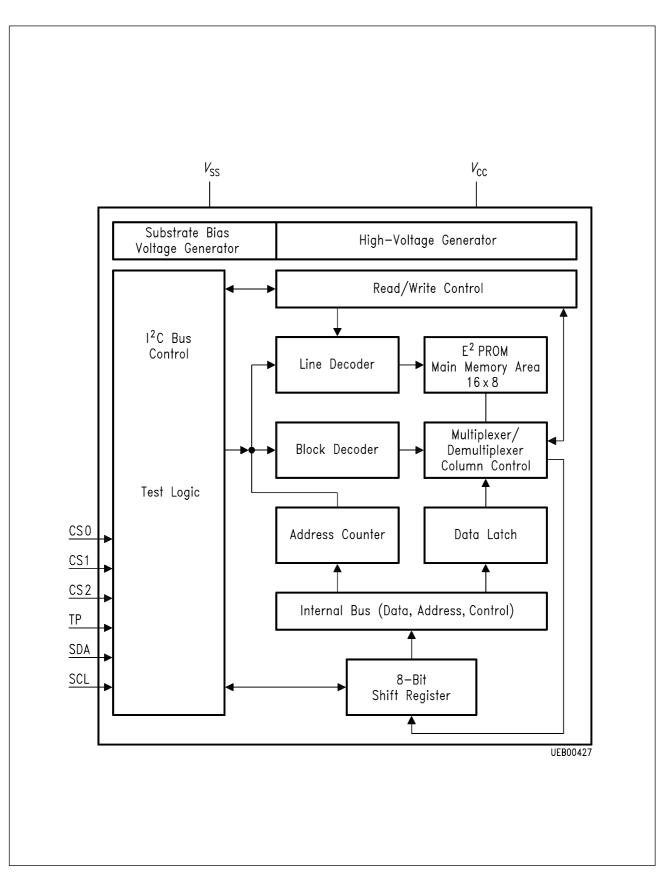

### **Block Diagram**

## Absolute Maximum Ratings

| Parameter                       | Symbol           | Li    | Unit |     |

|---------------------------------|------------------|-------|------|-----|

|                                 |                  | min.  | max. |     |

| Supply voltage                  | V <sub>CC</sub>  | - 0.3 | 6    | V   |

| Input voltage                   | VI               | - 0.3 | 6    | V   |

| Power dissipation               | P <sub>D</sub>   |       | 130  | mW  |

| Storage temperature             | T <sub>stg</sub> | - 40  | 125  | °C  |

| Thermal resistance (system-air) | R th SA          |       | 100  | K/W |

| Junction temperature            | Ti               |       | 85   | C   |

## **Operating Range**

| Supply voltage      | V <sub>CC</sub> | 4.75 | 5.25 | V  |

|---------------------|-----------------|------|------|----|

| Ambient temperature | T <sub>A</sub>  | 0    | 70   | °C |

## Characteristics

*T*<sub>A</sub> = 25 °C

| Parameter      | Symbol          | Li   | Limit Values |      |    | Test Condition        |  |

|----------------|-----------------|------|--------------|------|----|-----------------------|--|

|                |                 | min. | typ.         | max. |    |                       |  |

| Supply voltage | V <sub>CC</sub> | 4.75 | 5.0          | 5.25 | V  |                       |  |

| Supply current | I <sub>CC</sub> |      |              | 20   | mA | $V_{\rm CC}$ = 5.25 V |  |

## Inputs

| Input voltages<br>SDA/SCL | V <sub>IL</sub> |     | 1.5             | V  |                   |

|---------------------------|-----------------|-----|-----------------|----|-------------------|

| Input voltages<br>SDA/SCL | V <sub>IH</sub> | 3.0 | V <sub>CC</sub> | V  |                   |

| Input currents<br>SDA/SCL | I <sub>H</sub>  |     | 10              | μA | $V_{IH} = V_{CC}$ |

## Outputs

| Output current SDA  | I <sub>QL</sub> |  | 3.0 | mA | $V_{\text{QL}} = 0.4 \text{ V}$     |

|---------------------|-----------------|--|-----|----|-------------------------------------|

| Leakage current SDA | I <sub>QH</sub> |  | 10  | μA | $V_{\text{QH}} = V_{\text{CC max}}$ |

## Inputs

| Input voltages<br>CS0/CS1/CS2 | V <sub>IL</sub>   |     |    | 0.2             | V   |                          |

|-------------------------------|-------------------|-----|----|-----------------|-----|--------------------------|

| Input voltages<br>CS0/CS1/CS2 | V <sub>IH</sub>   | 4.5 |    | V <sub>CC</sub> | V   |                          |

| Input currents<br>CS0/CS1/CS2 | I <sub>IH</sub>   |     |    | 100             | μA  | V <sub>CC</sub> = 5.25 V |

| Clock frequency               | f <sub>SCL</sub>  |     |    | 100             | kHz |                          |

| Reprogramming duration        | t <sub>PROG</sub> |     | 10 | 20              | ms  | erase and write          |

| Input capacity                | Cl                |     |    | 10              | pF  |                          |

| Total erase                   | t <sub>GL</sub>   |     |    | 20              | ms  | CS2 = open               |

## **Application Circuit**

## **Application Circuit**

Semiconductor Group

## Operation States of the I<sup>2</sup>C Bus

#### Figure 1 Read Access Short Form

## Figure 2 Timing Conditions for the I<sup>2</sup>C Bus (high-speed mode)

| Parameter                                                             | Symbol               | Lin  | Unit |    |  |

|-----------------------------------------------------------------------|----------------------|------|------|----|--|

|                                                                       |                      | min. | max. |    |  |

| Minimum time the bus must be free before a new transmission can start | t <sub>BUF</sub>     | 4.7  |      | μs |  |

| Start condition hold time                                             | t <sub>HD; STA</sub> | 4.0  |      | μs |  |

| Clock low period                                                      | t <sub>LOW</sub>     | 4.7  |      | μs |  |

| Clock high period                                                     | t <sub>HIGH</sub>    | 4.0  |      | μs |  |

| Start condition set-up time,<br>only valid for repeated start code    | t <sub>SU;</sub> STA | 4.7  |      | μs |  |

| Data set-up time                                                      | t <sub>SU; DAT</sub> | 250  |      | ns |  |

| Rise time of both the SDA- and SCL-line                               | t <sub>R</sub>       |      | 1    | μs |  |

| Fall time of both the SDA- and SCL-line                               | t <sub>F</sub>       |      | 300  | ns |  |

| Stop condition set-up time                                            | t <sub>SU; SPO</sub> | 4.7  |      | μs |  |

| Hold time data                                                        | t <sub>HD; DAT</sub> | 0*)  |      |    |  |

\*) Note that a transmitter must internally provide at least a hold time to bridge the undefined region (max. 300 ns) of the falling edge of SCL.

#### Figure 3 Programming Control word input

#### Figure 4 Read

Control word input read a) complete (with word address input)

AutoincrementAm = 0before stop conditionAm = 1

## **Control Word Table**

| Clock No. | 1  | 2  | 3  | 4  | 5   | 6   | 7   | 8  | 9   | (Acknowledge)  |

|-----------|----|----|----|----|-----|-----|-----|----|-----|----------------|

| CS/E      | 1  | 0  | 1  | 0  | CS2 | CS1 | CS0 | 0  | 0   | through memory |

| CS/A      | 1  | 0  | 1  | 0  | CS2 | CS1 | CS0 | 1  | 0   | through memory |

| WA        | 0  | A6 | A5 | A4 | A3  | A2  | A1  | A0 | 0   | through memory |

| DE        | D7 | D6 | D5 | D4 | D3  | D2  | D1  | D0 | 0   | through memory |

| DA        | D7 | D6 | D5 | D4 | D3  | D2  | D1  | D0 | 0/1 | through master |

## **Control Word Input Key**

| CS/E        | Chip select for data input into memory    |

|-------------|-------------------------------------------|

| CS/A        | Chip select for data output out of memory |

| WA          | Memory word address                       |

| DE          | Data word for memory                      |

| DA          | Data word read out of memory              |

| D0 to D7    | Data bits                                 |

| ST          | Start condition                           |

| SP          | Stop condition                            |

| As          | Acknowledge bit from memory               |

| Am          | Acknowledge bit from master               |

| CS0/CS1/CS2 | Chip select bits                          |

| A0 to A6    | Memory word address bits                  |

|             |                                           |